EatonCTX210607

Ejemplo resuelto de pruebas adecuadas

Los transformadores inversores de lámpara fluorescente de cátodo frío (CCFL) se utilizan ampliamente para convertir un suministro de CC bajo en CA de alto voltaje para controlar, por ejemplo, las luces de fondo de las pantallas LCD.

Emplean una variante de la tecnología SMPS para conmutar la CC mediante transistores (en una configuración push-pull) a altas frecuencias (40-80 kHz en nuestro ejemplo) al primario.

Se utiliza un devanado de retroalimentación para proporcionar retroalimentación positiva para hacer que el circuito oscile.

Por lo general, el devanado secundario está diseñado deliberadamente para tener una inductancia de fuga establecida, que luego resuena con un capacitor en el secundario para accionar el tubo de iluminación.

Como el transformador es una parte integral del funcionamiento del circuito, la medición de parámetros como la inductancia de fuga es importante, así como los parámetros habituales de resistencia del devanado y relación de espiras. El transformador también necesita proporcionar aislamiento, especialmente porque el circuito primero genera un voltaje de "encendido" más alto para encender el tubo, antes de establecerse en un estado de funcionamiento constante.

EatonCTX210607

Eaton fabrica una variedad de transformadores CCFL versátiles para estas operaciones. Aquí, examinaremos el CTX210607.

Tenga en cuenta que el secundario está enrollado en 4 secciones.

Esto es para que la caída de voltios por vuelta se distribuya en 4 áreas separadas, lo que mejora el aislamiento entre devanados bajo las altas diferencias de potencial sin tener que recurrir a cables muy aislados.

Las bobinas primaria y de retroalimentación también están separadas. Esta separación controla la introducción deliberada de la inductancia de fuga discutida anteriormente.

Esquema CTX210607

La representación del software AT Editor de la pieza se muestra aquí a la izquierda.

Esquema del editor AT

El paquete del transformador tiene un diseño de montaje en superficie estándar y, como tal, no es adecuado para pines Kelvin.

El dispositivo que se muestra aquí es un casquillo de fuerza de inserción cero (ZIF) en el que se cierran pares de cuchillas en cada pasador desde un lado.

Esto tiene la ventaja de no someter la pieza a ninguna tensión mecánica y al mismo tiempo mantener un verdadero contacto Kelvin con cada devanado.

ZIF (enchufe de inserción cero) en el dispositivo 91-184

ZIF (enchufe de inserción cero) en el dispositivo 91-184

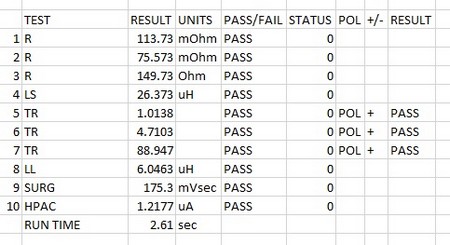

Primero se verifican las resistencias del devanado para validar la continuidad y la conexión.

A esto le sigue una verificación de inductancia en la frecuencia de operación en el primario.

A esto le siguen tres comprobaciones de las relaciones de espiras; mitad primaria a mitad primaria, primaria a retroalimentación y primaria a secundaria.

Tenga en cuenta que la última prueba se realiza energizando el secundario, ya que para una precisión óptima es mejor energizar el devanado con la mayor cantidad de vueltas.

Luego probamos la inductancia de fuga entre primario y secundario; encontramos que la fuga es aproximadamente el 25% de la inductancia primaria, ya que probablemente sea un factor de diseño deliberado en la operación del circuito LC de salida.

Para ello hemos utilizado límites porcentuales en torno a un valor nominal de LL, en lugar de comprobar que LL está justo por debajo de un máximo, como suele ser el caso.

Como el secundario está hecho de alambre fino y está sujeto a altos voltajes e incluso voltajes de "encendido" más altos para iniciar el tubo de gas, a continuación usamos la prueba SURG para verificar si hay debilidades en la bobina entre devanados. Esto se realiza inyectando pulsos de alto voltaje y midiendo la característica caída del timbre en el devanado secundario. Para nuestros límites se selecciona un nominal empírico de un transformador en buen estado. Cualquier rotura del aislamiento provocará una pérdida de energía y, por tanto, una respuesta de deterioro diferente.

Consulte el enlace al final de esta sección para obtener más información sobre las pruebas SURGE.

Finalmente, se utiliza una prueba HI POT a 2 kV CA para verificar el aislamiento primario al secundario.

# | Prueba | Descripción | Pines y condiciones | Razón |

| 1 | R | resistencia CC | pin 1-3, límites <135 mOhms | Para comprobar, la resistencia total del devanado primario está por debajo de un máximo. También actúa como control del calibre correcto del cable y de la buena terminación. |

| 2 | R | resistencia CC | pin 4-5, límites <100 mOhms | Para comprobar que la resistencia del devanado de retroalimentación está por debajo de un máximo. También actúa como control del calibre correcto del cable y de la buena terminación. |

| 3 | R | resistencia CC | pin 10-6, límites <175 ohmios | Para comprobar que la resistencia del devanado secundario esté por debajo de un máximo. También actúa como control del calibre correcto del cable y de la buena terminación. |

| 4 | LS | Inductancia en serie | Pin 1-3, 100 mV, 20 kHz, nominal 27 uH +/- 10 % (según las especificaciones publicadas) | Inductancia vista por el primario. Para comprobar el número correcto de vueltas y el correcto funcionamiento del material del núcleo. |

| 5 | TR | Relación de vueltas | Energice los pines 1-3, 100 mV 40 kHz, verifique que la relación de vueltas y la fase 1-2:2-3 sean 1:1 +/- 5% | Para verificar la relación correcta de devanados entre las dos mitades del grifo primario al central. |

| 6 | TR | Relación de vueltas | Energice los pines 1-3, 100 mV 40 kHz, verifique que la relación de vueltas y la fase 1-3:4-5 sean 4,6:1 +/- 5% | Para verificar la relación correcta de los devanados desde todo el devanado primario hasta el de retroalimentación. |

| 7 | TR | Relación de vueltas | Energice los pines 10-6, 100 mV 10 kHz, verifique que la relación de vueltas y la fase 10-6:1:3 sean 86:1 +/- 5% | Comprobar la relación correcta de los devanados del secundario al primario. El devanado con más vueltas se energiza, ya que es la mejor práctica para lograr una precisión óptima. |

| 8 | LL | Inductancia de fuga | Pines 1-3 Alto, Pines 10-6 Bajo, 100 mV, 40 kHz, verifique que la fuga esté por debajo de 6,5 uH | Verificar que la fuga esté por debajo del límite especificado como validación de la correcta colocación y funcionamiento de los devanados. |

| 9 | SURG | Prueba de estrés por sobretensión | Energice los pines 10-6, 4000 V, 5 pulsos. Compruebe que el producto mVs sea 166 mVs +/- 30% | Para comprobar si hay puntos débiles en el aislamiento secundario entre vueltas, para demostrar la longevidad de la pieza durante su vida operativa. |

| 10 | HPAC | AC Hi-Pot | 2 kV CA, 50 Hz, 1 segundo, pines 1,2,3,4,5 alto, pines 10,6 LO. Compruebe la corriente <15 mA | Para comprobar el aislamiento según la hoja de datos. |

| AT5600 Tiempo de ejecución 2,61 segundos | ||||

| (Tiempo de ejecución del AT3600 5,49 segundos) |

Notas:

Como la inductancia de fuga se rige por la relación de vueltas, la respuesta del núcleo (ya cubierta por TR y LS) y el posicionamiento físico de los devanados, algunos clientes (que utilizan métodos de devanado automático) pueden tener suficiente confianza en el posicionamiento de los devanados como para auditar este parámetro solo ocasionalmente. , en lugar de cada parte probada.